去年の暮れからFPGAをverilogで設計するという仕事に没頭しておりました。FPGAは、Xilinxから発表された当時(30年くらい前?)、新しいもの好きの私は、その頃高価なFPGAでトリプルポートのDRAMコントローラを画像処理用に作りました。ASICで作るよりは、FPGAで作るほうが、問題が起きた時に変更できるという利点もありましたが、高価でしたし、ゲート規模もPLDのお化けというような感じでたいしたものではなかったですが、結構設計に苦労しました。その当時まだ、論理合成なんていう便利なツールはなかったので、回路図レベルでまず設計しそれをFPGAエディターにCLBの中身を展開していくというなんとも大胆な方法で設計したものです。

回路図をのままを設計ツールで論理合成した場合、その当時のパソコン(486レベル?)では、丸1日かかるというもので、使い物にならないというのがその理由でした。それからFPGAの設計からしばらく離れておりました。

2012年は、verilogでの本格的な設計をはじめるきっかけとなりました。結構大規模なFPGA(xilinx)の設計で、spartan6のお世話になりました。技術の進歩は、すごいものです。しばらくFPGAから離れていただけで、タイムマシンで未来に来たかのごとく論理合成の時代は進歩していました。

いろいろはまるところがありましたが、今回最も冷や汗を掻いたところは、最終段シミュレーションも大体終わり、論理合成、配置配線をしようとした時にデバイスに入りきらないというエラーが出たときです。もうボードの実装も上がり、デバイスの変更はできない状態でした。最初の想定では、デバイスの選定は問題ないはずですが、何回条件をいろいろ変えてもできなくて、悩んだのですが、聞いてみるとブロックRAMを想定して設計している部分を、論理合成ツールがブロックRAMと認識せずにCLBでRAMを構成してしまっていた事が原因でした。

論理合成・配置配線で問題が出た場合は、ISEですと xxx.par とxxx.syr を、Planaheadですと xxx.srp とxxx.mrp を見て期待通りにブロックRAMを使って論理合成できているかを確認できます。期待するブロックRAMでできていない場合は、シュミレーションでは、動作するのですが、ブロックRAMとして認識できないような何らかの問題がRAM部の記述にあります。

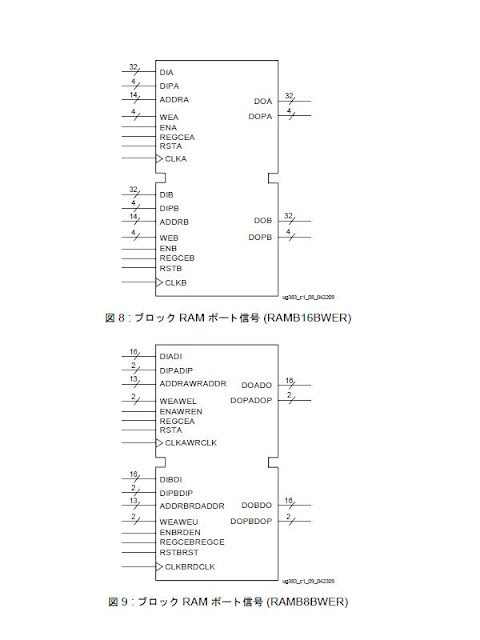

下記がブロックRAMの基本構造です。ブロックRAMの基本的な構造を理解する事で、この範囲を超えずに記述すればXSTは、ブロックRAMとして推論してくれます。完全な非同期のデュアルポートRAMを構成できます。IPブロックとして記述する方法もありますが、verilogで推論させたほうがスマートです。

心配であればコーディング途中で一度論理合成を走らせる事をお勧めします。後になって冷や汗を掻くよりは、事前にリスクを回避できれば、デバッグの効率もアップします。間違った記述でロジックを書き進めてしまってからでは、後の変更がたいへんですし、時間の浪費です。

どうしてもだめな場合は、(* RAM_STYLE="BLOCK" *)制約を追加する事で推論できるようになる可能性があります。基本的に上記ブロック構造を守っていればどんな複雑なロジックにしてもXSTは、ちゃんとブロックRAMとして推論してくれます。

あたりまえのことですが、1つのデータポートにアクセスできるアドレスは1つです。この理解さえできていればブロックRAMは、攻略できます。

XSTがブロックRAMとして推論しない認識しないと困られている皆様がんばってください。幸運を祈ります。

0 件のコメント:

コメントを投稿